パワー半導体が直面する2大課題

パワーエレクトロニクスの高電力密度化が進む中、パワー半導体デバイスの設計者が常に直面する2つの根本的な課題があります。それが「熱」と「ノイズ」です。

SiCやGaNといった次世代半導体は、Si(シリコン)に比べてスイッチング速度が大幅に向上しました。しかし、高速スイッチングは必然的に急峻なdv/dtとdi/dtをもたらし、EMI(電磁干渉)ノイズを増大させます。同時に、小型化・高出力化によって単位面積あたりの発熱密度も増加の一途をたどっています。

従来のアプローチとその限界

従来の対策は概ね以下のようなものでした:

| 課題 | 従来の対策 | 限界 |

|---|---|---|

| 熱 | 大型ヒートシンク、ファン冷却、TIM材 | 体積増大、信頼性低下 |

| ノイズ | スナバ回路、フィルタ、シールド | 部品点数増、コスト増 |

これらの対策は効果がある反面、「小型化」「コスト削減」「高信頼性」という市場要求とトレードオフの関係にあります。

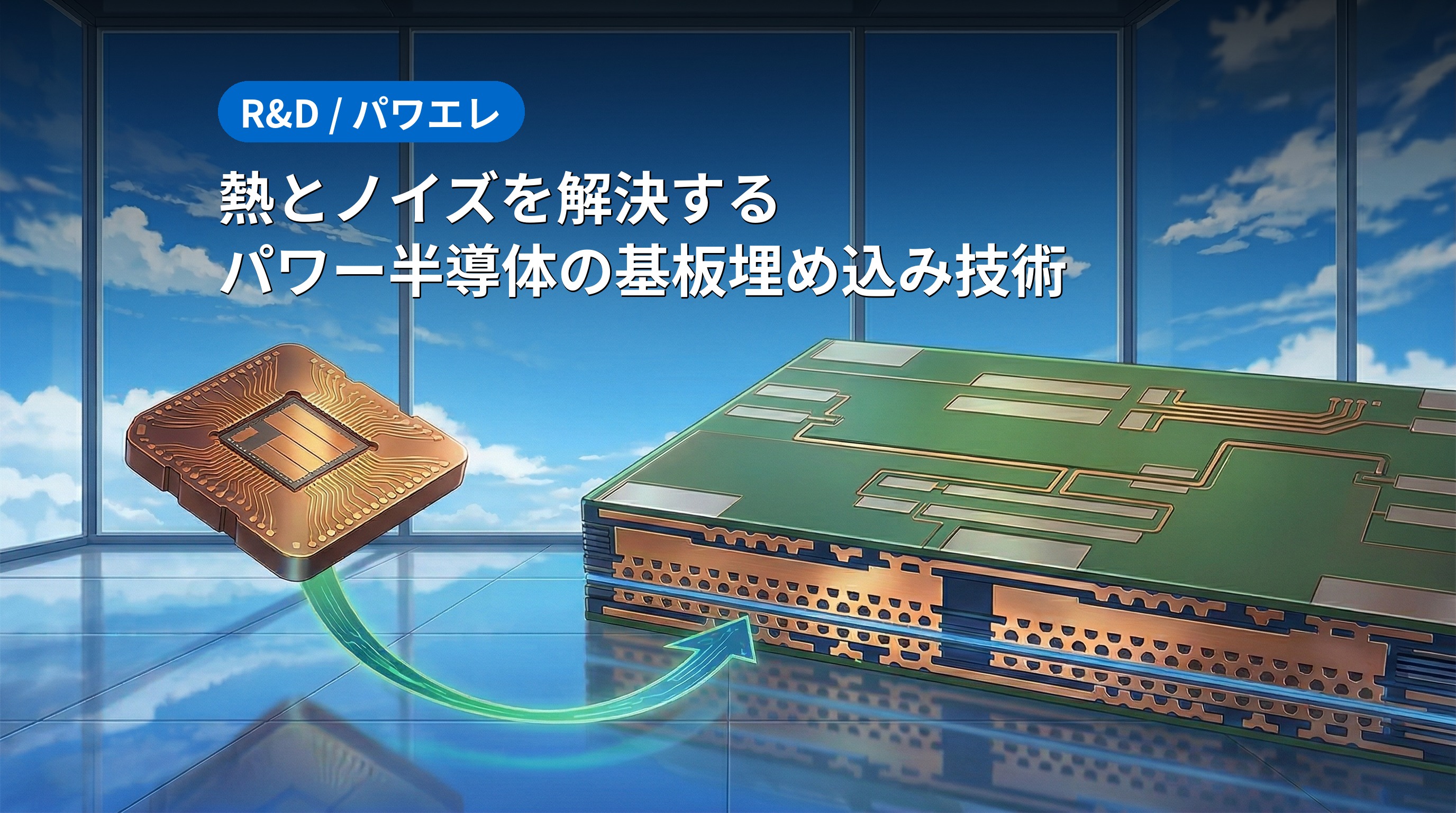

基板埋め込み技術とは

Link T&Bが取り組む「基板埋め込み技術」は、パワー半導体チップをプリント基板(PCB)の内層に直接埋め込む実装方式です。このアプローチにより、従来の「基板表面にチップを搭載する」という常識を覆します。

技術のポイント

- 配線インダクタンスの極小化:チップと配線パターンの距離が物理的に最短化されるため、寄生インダクタンスが劇的に低減。スイッチングノイズの根本原因を抑制します。

- 両面放熱の実現:チップの上下両面から基板の銅層を通じて放熱できるため、片面放熱に比べて熱抵抗を大幅に低減できます。

- モジュールの薄型化:チップが基板内部に収まるため、表面実装型に比べてモジュール全体の高さを削減できます。

従来実装との比較

| 項目 | 従来実装(表面実装) | 基板埋め込み |

|---|---|---|

| 配線インダクタンス | 数nH〜十数nH | 1nH以下 |

| 放熱経路 | 片面(底面のみ) | 両面 |

| モジュール高さ | 5〜15mm | 2〜5mm |

| EMIノイズ | フィルタで対処 | 根本的に抑制 |

今後の展望

基板埋め込み技術は、EV用インバータ、データセンター用電源、産業用モータドライバなど、高電力密度が求められるあらゆる分野への適用が期待されています。

Link T&Bは、本技術の研究開発を引き続き推進し、パワーエレクトロニクスの更なる高性能化に貢献してまいります。